Focus

The group is active in the ARPLab laboratory of the Politecnico di Milano and carries out research in the field of integrated circuit and system design (ASIC) in modern nanoscale silicon processes. The scaling of CMOS technology involves a degradation of some of the performances of the analog blocks such as gain, matching or noise. On the other hand, however, scaling makes it possible to digitally process signals at progressively higher speed, and with lower dissipation and area occupation. The design of high-performance ASICs therefore requires a paradigm shift, whereby digital processing is put at the service of each single block or analog sub-system to efficiently improve its performance, compensating in real time for variations in environmental parameters and system. This is based on the use of adaptive filtering and machine learning techniques and allows to increase the scalability and energy efficiency of integrated systems, adopting the so-called minimalist approach to the design of analog blocks. On these topics, the group has two active Joint Research Platforms with Infineon Technologies and STMicroelectronics, respectively, as well as active collaborations with other universities, research centers and companies. The main research interests are in the field of frequency synthesizers, analog/digital converters (ADCs) and DC/DC converters.

Most relevant research achievements

- Design of giga-samples-per-second analog-to-digital converters for high-capacity wireless systems

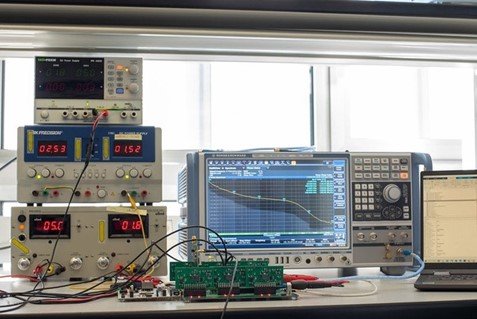

The group has achieved important results in the creation of analog-to-digital converters (ADC) at GigaSample/second (GS/s) in CMOS. In particular, an 8-core time-interleaving successive approximation converter (SAR) has been conceived and fabricated, reaching a bandwidth of 0.92 GHz and 9.2-bit equivalent bits of resolution (IEEE J. Solid-State Circuits, 2024). While time-interleaving technique allows several energy-efficient ADCs to be combined to create a high-speed converter, it introduces unwanted spurious signals into the output spectrum, limiting the SFDR of the converter, due to gain and offset mismatches between the ADCs, as well as non-ideality in the distribution of clock, supply and reference voltage. Both purely analog techniques and digital algorithms (implemented in the same converter chip) were therefore designed and implemented in TSMC's 28-nm CMOS, which correct these non-idealities or in some cases their effects. The entire converter including the correction algorithms has a consumption of less than 120 mW. Currently, research is active in the exploration of hybrid types of ADC cores, such as those based on noise-shaping SAR, pipeline-SAR, flash-aided SAR, with the aim of increasing bandwidth and/or resolution and reducing power consumption.

- Design of low phase-noise frequency synthesizers for high-capacity wireless communication systems

Over the years, the research group has developed consolidated experience in the frequency synthesis field. It has proposed numerous innovations that have significantly improved the state of the art, and, in this field, it is recognized as a center of excellence internationally. The most recent results concern high-performance frequency synthesizers based on phase-locked loops (PLLs), of the fractional-N type (i.e. with a non-integer ratio between output and reference frequency), to be used as local oscillators (LO) in high-capacity wireless communication systems (5G/6G). Prototypes made in 28-nm CMOS, operating between 8 and 12 GHz, have reached absolute jitter values lower than 80 fs rms and spurious levels lower than -70 dBc (even for near-integer channels), with power dissipations less than 18 mW (IEEE J. Solid-State Circuits, 2023). Such levels of spuriousness were made possible by adopting digital calibrations operating in the background that operate in real time on cancellations or non-ideality corrections of the analog or mixed-signal blocks. The group obtained the important recognition of the "2023 Jan Van Vessem Award for Outstanding European Paper" at the IEEE International Solid-State Circuits Conference (ISSCC) for the paper (by Dartizio et al.) "A 76.7fs-Integrated-Jitter and -71.9 dBc In-Band Fractional-Spur Bang-Bang Digital PLL Based on an Inverse-Constant-Slope DTC and FCW Subtractive Dithering”.

- Design of low-power wireless transmitters for IoT systems

The group works in the design of low-power wireless transmitters. The reference applications are those of Bluetooth low energy (BLE), a wireless communication technology used in wearable devices and other mobile devices that transmit small quantities of data at short distances, WiFi (now version 7) which allows you to transmit greater quantities of data for higher consumption, and in general the technologies that can enable the idea of Internet-of-things (IoT). In this area, the group has achieved important results by creating a frequency synthesizer, based on an innovative fractional multiplying delay-locked loop (MDLL) architecture in the 1.6-3.0 GHz range, which achieves absolute jitter lower than 400 fs rms and consumption of approximately 3 mW in 65-nm CMOS process (IEEE J. of Solid-State Circuits, 2019). The group also designed and implemented a 20 Mb/s GMSK/QPSK modulator based on direct modulation of a fractional digital PLL with two-point injection scheme, in 65-nm CMOS, operating at 3.6 GHz with consumption of 0.25 nJ/ bit and EVM less than -36 dBc (IEEE J. Solid-State Circuits, 2012). A second modulator prototype in 28-nm CMOS (IEEE Solid-State Circuits Letters, 2020) made it possible to reach a bit rate of 250 Mb/s by modulating a carrier at 14 GHz, with EVM lower than -42 dB and consumption of 0.13 nJ/bit. The group also designed a digital power amplifier (DPA) in 28-nm FD-SOI CMOS at 900 MHz with 20 dBm output power. The group is currently active in the design of very low power (<0.5mW) frequency synthesizers for BLE applications, based on digital PLLs with LC oscillators.

- Millimeter wave circuit design for wireless systems

The group is active in the realization of millimeter-wave integrated circuits in CMOS and SiGe BiCMOS technology. In particular, a 30-GHz fractional PLL prototype was designed and fabricated in TSMC's 65-nm LP CMOS with performance beyond the state of the art, presented at the ISSCC conference in 2019. The group participated in the European H2020 project called “TARANTO”, contributing to the design of an E-band transceiver (71-76 and 81-86 GHz) for wireless backhauling in SiGe BiCMOS55 technology by STMicroelectronics, and to the European Horizon Europe project called "SHIFT", currently underway, collaborating to the design of a D-band transceiver (141-175 GHz) in SiGe BiCMOS55X technology from STMicroelectronics. In SHIFT, the group is working on the design and characterization of low-power E-band frequency multipliers, based on an innovative digitally-calibrated architecture, and of a frequency synthesizer in the 10-12 GHz range with very low absolute jitter values ( <10 fs rms) and phase noise (<-132 dBc/Hz at 1 MHz offset from the carrier). These circuits will be able to enable high-capacity millimeter wave communication systems with multilevel modulations (even up to 4096 QAM).

- Design of phased-array architectures and chirp signal generators for radar applications

Significant results have been achieved in the field of radar systems for autonomous driving systems. In particular, the group has designed some prototypes in 28-nm CMOS technology of innovative chirp signal generators, i.e. sinusoidal signals whose frequency follows the trend of a sawtooth or a triangular wave, essential for the creation of an FMCW radar. In such applications, the amplitude of the FM modulation wave, its slope, its linearity and the phase-noise of the generator are determining aspects in the spatial resolution performance of the radar itself and the ability to discriminate close objects. The group has introduced, in a 10-GHz digital PLL architecture in 28-nm CMOS, modulated by a two-point signal injection, an innovative pre-distortion technique of the digitally controlled oscillator (DCO) with parabola sections and adaptive breakpoints, which minimizes digital hardware complexity and achieves 150-kHz FM error on a sawtooth chirp with 680-MHz bandwidth and 1-us minimum repetition period (IEEE ISSCC Conference, 2024). The group proposed the architecture based on “Localized LO phase shifting” for the creation of multi-antenna or “phased array” transceivers. In this architecture, the phase shift, necessary for the "beam steering" of the transmitted and received wave, is achieved through the phase shift introduced by an array of localized LO generators, synchronized by a quartz oscillator (IEEE ISSCC, 2021).

- Study of phase noise generation mechanisms in electronic oscillators

Another active area in which the group has provided significant results is the study of phase-noise generation mechanisms in electronic oscillators, frequency multipliers and dividers. A theoretical description of the mechanisms for converting low-frequency flicker noise into radio-frequency noise in CMOS oscillators was introduced, and effective circuit solutions to reduce this conversion were proposed and experimentally demonstrated, which improved the state of the art (IEEE ISSCC Conference, 2010). More recently, the group has developed a theory of phase noise in voltage-biased oscillators (IEEE Trans. on Microwave Theory and Techniques, 2013), pulsed injection-locked oscillators (IEEE Trans. on Circuits and Systems-I, 2014), Periodically on/off oscillators (IEEE Trans. on Circuits and Systems-I, 2023) used in some architectures for frequency generation in the millimeter wave range.

- Design of inductive DC/DC converter circuits with time-based control

The traditional approach to the analog control of inductive DC/DC converters suffers from some limitations related to the limited gain-bandwidth product of the error amplifier and the limited operating range of the PWM modulator. In time-based control, the voltage information is directly encoded in a phase delay of a periodic signal. This allows you to naturally generate PWM modulation using a simple phase discriminator. This emerging approach to control has been studied and applied by the research group to the design of DC/DC converters integrated in BCD technology for applications in mobile and wearable devices, where high efficiency, high power density, and low power consumption at low load currents are required. In particular, the group has obtained significant results in the design and implementation of the first boost converter (from 2.5-4.5V to 5V) with "time-based" control, created for the power supply of AMOLED displays with a maximum current of 0.8 A, efficiency peak of 96% and low-load (50 mA) efficiency of 90%, demonstrating a controller area reduction of approximately 40% in 180-nm BCD technology (IEEE Trans. on Power Electronics, 2023). Another important result was the implementation of a buck converter (from 5-32V to 3.3V) with "time-based" control, for industrial applications, with a current of 1.4 A and a quiescent current (at zero load) of 14 uA, in 180-nm BCD technology (IEEE Trans. on Circuits and Systems-I, 2024).

- Design of resonant switched capacitance DC/DC converter circuits

Switched-capacitor DC/DC converters rely on capacitors to transfer energy but suffer from switching losses. Resonant converters introduce a relatively small value inductor that resonates with the capacitors and enables the zero-current switching (ZCS) technique to achieve high efficiency and power density. In this field, the group has devised an innovative interleaved Dickson converter topology with regulated conversion from 12 to 3V, which achieves a power density beyond the state of the art (0.53 W per square mm) with a load current of 5 A and peak efficiency of 94.4%, thanks also to the use of resonant inductors made through the inductive parasitics of the PCB (IEEE Trans. on Power Electronics, 2024). The concept of resonant converters finds natural application in "intermediate-bus converters" for modern data centers, in which to mitigate copper losses and respond to the growing power needs of the CPU/GPU, there is a tendency to progressively raise the bus voltage. This however requires a high conversion factor from bus voltage to final voltage. The research group, in this sector, has obtained an important result, designing and creating a hybrid-resonant switched tank converter (HRSTC) prototype which operates a voltage conversion (unregulated) from 48 to 3.4 V with an output current of up to at 260 A, peak efficiency of 96.6% and power density of 920 W per cubic inch (IEEE APEC conference, 2024) and an STC prototype with sigma buck-boost regulation, which achieves conversion from 48 to 12 V with power of peak of 720 W, at efficiency of 97.6% (at 30 A) and power density of 900 W per cubic inch (IEEE APEC conference, 2024).

- Front-end project for MEMS sensors

Another area in which the group operates is that of the design of CMOS microsystems for sensors, both in the field of neuronal signal detection and in the field of accelerometers, gyroscopes and magnetometers based on micro-mechanical systems (MEMS). In these sectors, the challenge arises of signal acquisition and analog/digital conversion of the signal with low noise and low dissipated power. The group, in collaboration with the DEIB’s "Microsensors and intelligent microsystems" group, has obtained an important result in the field of FM modulated MEMS sensors, designing and implementing a frequency-digital converter with a dynamic range (DR) of 140 dB in 130-nm CMOS technology (IEEE Trans. on Instrumentation and Measurement, 2023).