Research Area:

Responsible:

Participants:

Research Lines:

Project abstract

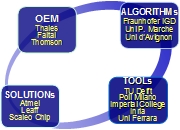

hArtes aims at laying the foundation for a new holistic (end-to-end) approach for complex real-time embedded system design, with the latest algorithm exploration tools and reconfigurable hardware technologies. The proposed approach addresses, for the first time, optimal and rapid design of embedded systems from high-level descriptions, targeting a combination of embedded processors, digital signal processing and reconfigurable hardware. We will develop modular and scalable hardware platforms that can be reused and re-targeted by the tool chain to produce optimized real-time embedded products.

The results will be evaluated using advanced audio and video systems that support next-generation communication and entertainment facilities, such as immersive audio and mobile video processing.

Innovations of our approach include:

- support for both diagrammatic and textual formats in algorithm description and exploration;

- a framework that allows novel algorithms for design space exploration, which aims at automating design partitioning, task transformation, choice of data representation, and metric evaluation for both hardware and software components;

- a system synthesis tool producing near-optimal implementations that best exploits the capability of each type of processing element.

Project results

One of the most relevant outcomes of the project is the development of an open-source framework (PandA), parsing SystemC, C++/C specifications into graph-based representations containing information to implement the metrics-based analysis, partitioning and high-level synthesis algorithms (http://trac.elet.polimi.it/panda/).

Some of the analyses performed by PandA come from its integration in the GCC framework and some others are peculiar to embedded system design.

Papers published:

- F. Ferrandi, L. Fossati, M. Lattuada, G. Palermo, D. Sciuto, A. Tumeo, “Partitioning and Mapping for the hArtes European Project”, Workshop on “Directions in FPGAs and Reconfigurable Systems: Design, Programming and Technologies for adaptive heterogeneous Systems¬on¬Chip and their European Dimensions”, held during Design Automation and Test in Europe 2007 (DATE '07), Nice, Fra, April 2007.

- F. Ferrandi, L. Fossati, M. Lattuada, G. Palermo, D. Sciuto, A. Tumeo, “Automatic parallelization of sequential specifications for symmetric MPSoCs”, International Embedded Systems Symposium 2007 (IESS '07), Irvine, CA, USA, May 2007.