Area di ricerca:

Responsabile:

Linee di ricerca:

Sommario

The project aims at the development of the technology for very high density Non Volatile Memories for mass storage applications down to the 2X nm technology node. The field is receiving increasing attention, due to the explosion of portable multimedia applications, and is forecasted to exceed 40 Billion US$ total available market by 2010.

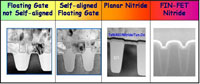

The dominant technology for this application is the floating gate NAND memory. However severe technological roadblocks (reduction in storage charge and electrostatic interference among neighboring cells) are limiting further scaling beyond the 32 nm node.

Charge trapping in dielectric layers seems to be a viable alternative to floating gate. The main challenge is the integration of the different new materials, like tunnel dielectric, trapping layer, top dielectric, metal gate at the target technology node and the achievement of an acceptable trade-off between functionality and reliability (e.g. charge retention and endurance).

The project will cover material development, cell architecture, modeling of material properties, trapping and conduction behavior in the dielectrics, metal gate materials. Starting on Jan 2008.

Risultati del progetto ed eventuali pubblicazioni scientifiche/brevetti

Initial studies will be performed on available technology 65-45nm to arrive to full process integration and realization of full arrays in a technology in the 28-36 nm range (the best achievable with available lithography) by two major European semiconductor manufacturers. It will include memory characterization and reliability testing, with the additional aim of defining standards and procedures for reliability assessment. Technology options for higher integration densities, for a given lithography node, will be investigated with the help of public research partners.

The final demonstrator will be a fully working memory array in the multi-gigabit range. The contributions of DEI’s researchers will be on:

- Modeling of cell electrical behaviour

- Cell characterization and reliability

- Array characterization and reliability

- Modeling of reliability characteristics

- Demonstration of multi-bit storage capabilities

- Training Programs