Area di ricerca:

Responsabile:

Linee di ricerca:

Sommario

La ricerca è mirata all’ideazione di tecnologie e all’implementazione di metodologie per il testing non invasivo di circuiti elettronici ULSI (Ultra Large Scale of Integration). L’apparato proposto si basa su misure sperimentali della luminescenza emessa spontaneamente dai circuiti integrati durante il loro funzionamento, con risoluzione temporale di pochi picosecondi. Altri scopi della ricerca sono la definizione e la validazione di modelli analitici e SPICE per la luminescenza da singoli transistori MOS soggetti ad elevati campi elettrici, per permettere mediante simulazioni CAD di prevedere l’andamento temporale della luminescenza e dei segnali elettrici all’interno del chip, per poter individuare difetti circuitali, malfunzionamenti o violazioni di specifiche. Il gruppo di ricerca ha sviluppato e realizzato:

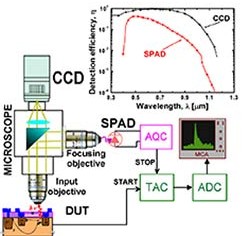

- microscopio per l’indagine ottica di circuiti integrati mediante rivelatori bidimensionali CCD (Charge-Coupled Devices) statici e SPAD (Single Photon Avalanche Diode) risolti temporalmente;

- modelli analitici e SPICE della luminescenza emessa, in funzione del punto di lavoro del transistore e dei parametri tecnologici di fabbricazione;

- metodologie di confronto tra misure sperimentali e simulazioni SPICE, per individuare malfunzionamenti circuitali;

- test e debug di chip reali.

Attualmente sono in corso collaborazioni con IBM, T.J. Watson Research Center, Yorktown Heights, USA, researchweb.watson.ibm.com/journal/rd/444/tsang.html Dr. Franco Stellari e STMicroelectronics – Agrate Brianza.

Risultati del progetto ed eventuali pubblicazioni scientifiche/brevetti

- “Tools for Contactless Testing and Simulation of CMOS Circuits” F. Stellari, F. Zappa and S. Cova Microelectronics Reliability, vol. 41, no. 11, 1801-1808 (Nov. 2001).

- “High-Speed CMOS Circuit Testing by 50ps Time-Resolved Luminescence Measurements” F. Stellari, F. Zappa, , S. Cova, C. Porta and J. C. Tsang IEEE Transactions on Electron Devices, vol. 48, no. 12, 2830-2835 (Dec. 2001).

- “Backside Flip-Chip testing by means of high-bandwidth luminescence detection” A. Tosi, F. Stellari, F. Zappa, and S. Cova Microelectronics Reliability, vol. 43, issue 9-11, 1169-1674, 2003.

- “CMOS Circuit Testing via Time-Resolved Luminescence Measurements and Simulations” F. Stellari, A. Tosi, F. Zappa, and S. Cova IEEE Transactions on Instrum. and Measurements, vol. 53, no. 1, 163-169, 2004.

- "Current crowding in faulty MOSFET: optical and electrical investigation" A. Tosi, F. Stellari, and F. Zappa Microelectronics Reliability, vol. 44, issue 9-11, Sep.-Nov. 2004, 1577-1581.

- "Implementation of TRE systems into Emission Microscopes" A. Tosi, M. Remmach, R. Desplats, F. Zappa, and P. Perdu Microelectronics Reliability, vol. 44, issue 9-11, Sep.-Nov. 2004, 1529-1534.

- “Innovative packaging technique for backside optical testing of wire-bonded chips” A. Tosi, F. Stellari, F. Zappa Microelectronics Reliability, Vol. 45, Issue 9-11, September - May, 2005, pp. 1493-1498.